COASt, an acronym for "cache on a stick", is a packaging standard for modules containing SRAM used as an L2 cache in a computer. COASt modules look like somewhat oversized SIMM modules. These modules were somewhat popular in the Apple and PC platforms during early to mid-1990s, but with newer computers cache is built into either the CPU or the motherboard. COASt modules decoupled the motherboard from its cache, allowing varying configurations to be created. A low-cost system could run with no cache, while a more expensive system could come equipped with 512 KB or more cache. Later COASt modules were equipped with pipelined-burst SRAM.

The standard was originally defined by Motorola to be between 4.33 and 4.36 inches (110 and 111 mm) wide, and between 1.12 and 1.16 inches (28 and 29 mm) high. It could be found in many Apple Macintosh in the early-to-mid-90s, but disappeared as the Mac moved to the PowerPC platform.

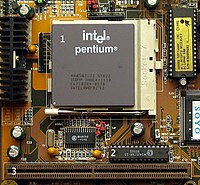

Intel also used the COASt standard for their Pentium systems, where it could be found as late as 1998 in Pentium MMX systems utilizing Intel chipsets such as 430VX and 430TX. Later, Intel combined this architecture with the CPU and created the Slot 1 CPU cartridge which contained both the CPU and separate cache chips.

The slot that the COASt module plugged into was named "CELP", or "card edge low profile", referring to the small circuit board and the conductors on its edge. It had 80 contacts on each side of a circuit board (for a total of 160), spaced 0.050" apart, plus an identification notch between contacts 42 and 43.

Operation

editCOASt modules provided either 256K or 512K of direct-mapped cache, organized as 8192 or 16384 lines of 32 bytes. A 64-bit data bus allowed the cache line to be transferred in a 4-cycle burst.

The modules contained 256K or 512K of fast pipeline burst SRAM, plus 8 or 11 bits of even faster static RAM per line to store the cache tags. (The module provides pins for 11 lines, but many motherboards and modules provided only 8.) Some variants (illustrated to the right) placed the tag RAM on the motherboard and only the main cache RAM was on the module.

Consider the 256K module first. An 8-bit tag allows caching memory up to 256 times the cache size, or 64 MiB. An 11-bit tag supports up to 512 MiB. Each cache line also has a valid bit and a dirty bit, stored in the cache controller. (16 Kbits, or 2 Kbytes, total size.)

A 512K module contains twice as many cache lines, and so requires one fewer tag bit to support the same cacheable memory size. The leftover tag bit is instead used to store the cache line dirty bit, and all 16 Kbits in the cache controller are used for valid bits.

References

edit- COASt Modules, PCGuide, April 17, 2001.

- Cache Module Physical Installation Procedure, PCGuide, April 17, 2001.

- Renn, Brian. The Cache Guide: What is COASt?, December 12, 1998.

- Accutek Microcircuit Corporation, 512KB Secondary Cache Module for the Pentium CPU and 82430 PCISETS, retrieved 2012-01-01. Supports 11-bit tag.

- Motorola (1996-12-09), 256K/512K Pipelined BurstRAM™ Secondary Cache Module for Pentium™ (PDF), retrieved 2012-01-01. Supports 8-bit tag only.